# Chapter 51 Cost Evaluation of Synchronization Algorithms for Multicore Architectures

Masoud Hemmatpour Politecnico di Torino, Italy

**Renato Ferrero** *Politecnico di Torino, Italy*

**Filippo Gandino** *Politecnico di Torino, Italy*

Bartolomeo Montrucchio Politecnico di Torino, Italy

Maurizio Rebaudengo Politecnico di Torino, Italy

# ABSTRACT

In a multicore environment, a major focus is represented by the synchronization among threads and processes. Since synchronization mechanisms strongly affect the performance of multithread algorithms, the selection of an effective synchronization approach is critical for multicore environments. In this chapter, the cost of the main existing synchronization techniques is estimated. The current investigation covers both hardware and software solutions. A comparative analysis highlights benefits and drawbacks of the considered approaches. The results are intended to represent a useful aid for researchers and practitioners interested in optimization of parallel algorithms.

## INTRODUCTION

One of the major issues in modern computer architecture is multicore design. Programmers have been urged to design innovative algorithms by exploiting multicore facilities. Synchronization, i.e., the technique adopted for coordinating threads or processes to have appropriate execution order, is one of the

DOI: 10.4018/978-1-5225-7598-6.ch051

main issues in programming on a multicore processor. In the literature, many synchronization techniques based on hardware and software have been proposed (Petrović, 2014; Yoo, 2013; McKenney, 1998). Modern computers provide special hardware instructions that allow to test and modify the content of a word atomically (e.g., the *cmpxchg* instruction of Intel) which can be used for synchronization of threads (Valois, 1995; Gao, 2007). Software techniques can synchronize threads without any dependency on hardware instructions (McKenney, 1998; Mellor-Crummey, 1991). One important aspect of a synchronization algorithm is its performance, which is evaluated in terms of overhead. In this study, the term cost is used to address an overhead of synchronization algorithm. The state-of-the-art approaches strive to increase the performance by reducing the cost of the synchronization. To the best of the authors knowledge a study to analyze the possible costs of synchronization mechanisms is absent. So, this chapter investigates the costs in the main steps of a synchronization mechanism, a discrete time Markov chain model of memory access cost is presented to evaluate the memory access overhead.

The remainder of this chapter is organized as follows. The primitives of the main synchronization algorithms are described in Section 2. Then, a theoretical evaluation of each cost and experimental results are presented in Section 3. Finally, some conclusions are described in Section 4.

## BACKGROUND

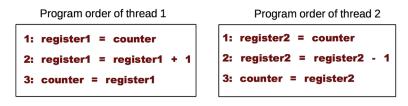

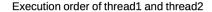

When threads are working simultaneously on a shared object, their synchronization should be managed properly, otherwise the instructions of different threads interleave on the shared object in a wrong way. For example, Figure 1 shows the program order of two threads that are working on the shared object counter (Silberschatz, 2006). Since one thread is incrementing the counter and another one is decrementing it, at the end, the counter is expected to have the initial value. However, as Figure 1 illustrates, there is a possible execution order of instructions that leads to an incorrect result.

Figure 1. Incorrect execution of the instructions order

```

1: register1 = counter

2: register1 = register1 + 1

3: register2 = counter

4: register2 = register2 - 1

5: counter = register1

6: counter = register2

```

15 more pages are available in the full version of this document, which may be purchased using the "Add to Cart" button on the publisher's webpage: www.igi-global.com/chapter/cost-evaluation-of-synchronization-algorithmsfor-multicore-architectures/214654

# **Related Content**

#### Efficient Rectenna Circuit for Wireless Power Transmission

Anurag Saxena, Paras Raizada, Lok Prakash Gautamand Bharat Bhushan Khare (2020). *Design and Optimization of Sensors and Antennas for Wearable Devices: Emerging Research and Opportunities (pp. 57-65).*

www.irma-international.org/chapter/efficient-rectenna-circuit-for-wireless-power-transmission/235782

#### The Impact of Mobility on Social and Political Movement

Nabil Harfoush (2012). *Mobile Technology Consumption: Opportunities and Challenges (pp. 138-167).* www.irma-international.org/chapter/impact-mobility-social-political-movement/60217

## Design and Development of Educational Multimedia: The Software Development Process for Mobile Learning

Ibrahim Arpaci (2016). Wearable Technology and Mobile Innovations for Next-Generation Education (pp. 147-165).

www.irma-international.org/chapter/design-and-development-of-educational-multimedia/149605

#### **Corporate Disclosure Measurement**

Md. Salah Uddin Rajiband Md. Qutub Uddin Sajib (2019). *Advanced Methodologies and Technologies in Network Architecture, Mobile Computing, and Data Analytics (pp. 489-501).* www.irma-international.org/chapter/corporate-disclosure-measurement/214638

### Secure Routing and Scheduling in Ad-Hoc Cognitive Radio Networks for Public Safety

Eric Chan-Tinand Qi Cheng (2014). *International Journal of Handheld Computing Research (pp. 44-60)*. www.irma-international.org/article/secure-routing-and-scheduling-in-ad-hoc-cognitive-radio-networks-for-publicsafety/124959